Lagarto: Desarrollo de procesadores Open ISA y S.O. Open Source

Una estrategia para impulsar el desarrollo de una industria nacional de TIC

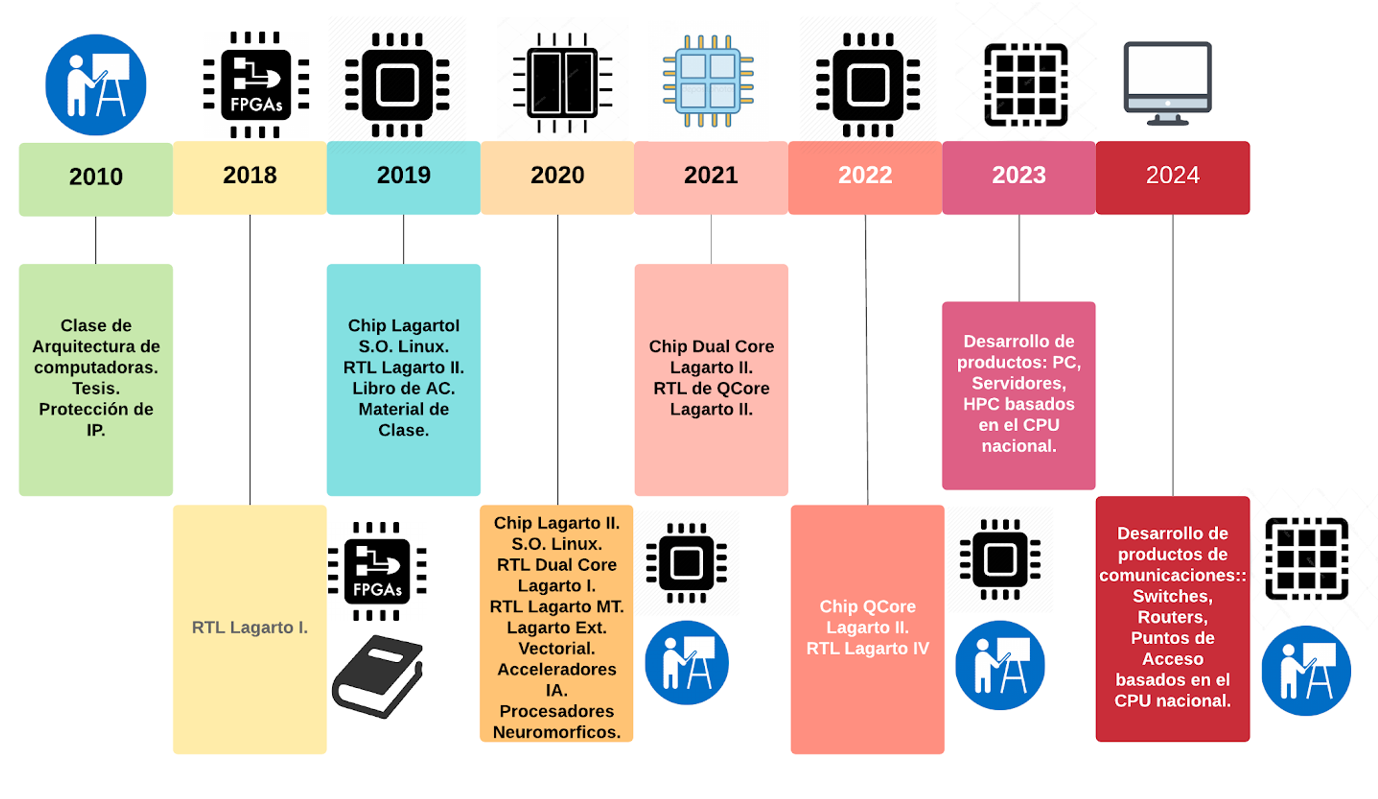

#RouteMap

El proyecto tiene un plan de ejecución como se muestra en la gráfica, para 2019 se ha fabricado el Chip del Procesador Lagarto I, de 64 bits RISC V en cooperación con el Centro de Supercomputación de Barcelona BSC, el Centro Nacional de Microtecnología CNM y la Universidad Politecnica de Cataluña UPC.

2021:

Segunda fabricación del Chip del Procesador Lagarto HUN (en BSC conocido como DVINO), y se finaliza la version RISC-V de Lagarto KA un procesador superscalar de 2 vias, y se inician pruebas a nivel RTL.

Tambien se comienza el desarrollo de semiconductores periféricos para computadoras y para sistemas de control. Puesta a punto del Sistema Operativo basado en Linux para Lagarto I.

2022:

Tercera fabricación del Chip de Lagarto I (incluye una VPU), se continúan las preubas presilicio del Procesador Lagarto KA, y Diseño a nivel RTL de una Jerarquia de Memoria para un SoC basado en cualquiera de los procesadores de la familia Lagarto.

2023:

Fabricación del Chip del Procesador Lagarto KA y adecuación del SoC en FPGA para realizar pruebas de la Jerarquia de Memoria y el boot de un Sistema Operativo Linux.

2024:

Pruebas de multinucleos basados en Lagarto HUN y KA a nivel RTL. adecuación del Sistema Operativo.

2025:

Desarrollo de productos basados en tecnología doméstica.

2021:

Segunda fabricación del Chip del Procesador Lagarto HUN (en BSC conocido como DVINO), y se finaliza la version RISC-V de Lagarto KA un procesador superscalar de 2 vias, y se inician pruebas a nivel RTL.

Tambien se comienza el desarrollo de semiconductores periféricos para computadoras y para sistemas de control. Puesta a punto del Sistema Operativo basado en Linux para Lagarto I.

2022:

Tercera fabricación del Chip de Lagarto I (incluye una VPU), se continúan las preubas presilicio del Procesador Lagarto KA, y Diseño a nivel RTL de una Jerarquia de Memoria para un SoC basado en cualquiera de los procesadores de la familia Lagarto.

2023:

Fabricación del Chip del Procesador Lagarto KA y adecuación del SoC en FPGA para realizar pruebas de la Jerarquia de Memoria y el boot de un Sistema Operativo Linux.

2024:

Pruebas de multinucleos basados en Lagarto HUN y KA a nivel RTL. adecuación del Sistema Operativo.

2025:

Desarrollo de productos basados en tecnología doméstica.