Lagarto: Desarrollo de procesadores Open ISA y S.O. Open source

Una estrategia para impulsar el desarrollo de una industria nacional de TIC

#Cores&Tools

Las herramientas EDA utilizadas para el diseño de procesadores estan basadas en Lenguajes de Descripción de Hardware HDL, (Verilog /System Verilog). Con estos lenguajes de alto nivel se modelan los bloques funcionales de las arquitecturas de procesadores y se sintetizan en dispositivos lógicos programables FPGA.

Las herramientas utilizadas para el desarrollo de Sistemas Operativos, estan basados Linux. Especialmente la distribución de Tizen es de mucho interés para el desarrollo de productos.

QEMU es una herramienta de simulación de un sistema de cómputo completo que incluye un sistema operativo y un procesador, ademas de los periféricos tradicionales de una computadora.

Las herramientas utilizadas para el desarrollo de Sistemas Operativos, estan basados Linux. Especialmente la distribución de Tizen es de mucho interés para el desarrollo de productos.

QEMU es una herramienta de simulación de un sistema de cómputo completo que incluye un sistema operativo y un procesador, ademas de los periféricos tradicionales de una computadora.

Quartus II es la herramienta EDA producida por Altera/Intel para el desarrollo, análisis y sintesis de los modelos electrónicos a nivel RTL.

Tizen es un Sistema Operativo móvil basado en Linuix, de código abierto y fléxible creado desde cero para abordar las necesidades de todas las partes interesadas del ecosistema de dispositivos móviles y conectados, incluidos los fabricantes de dispositivos, operadores móviles, desarrolladores de aplicaciones y proveedores de software independientes (ISV).

QEMU es un simulador de software abierto genérico de un sistema de cómputo completo que incluye un CPU y el Sistema operativo.

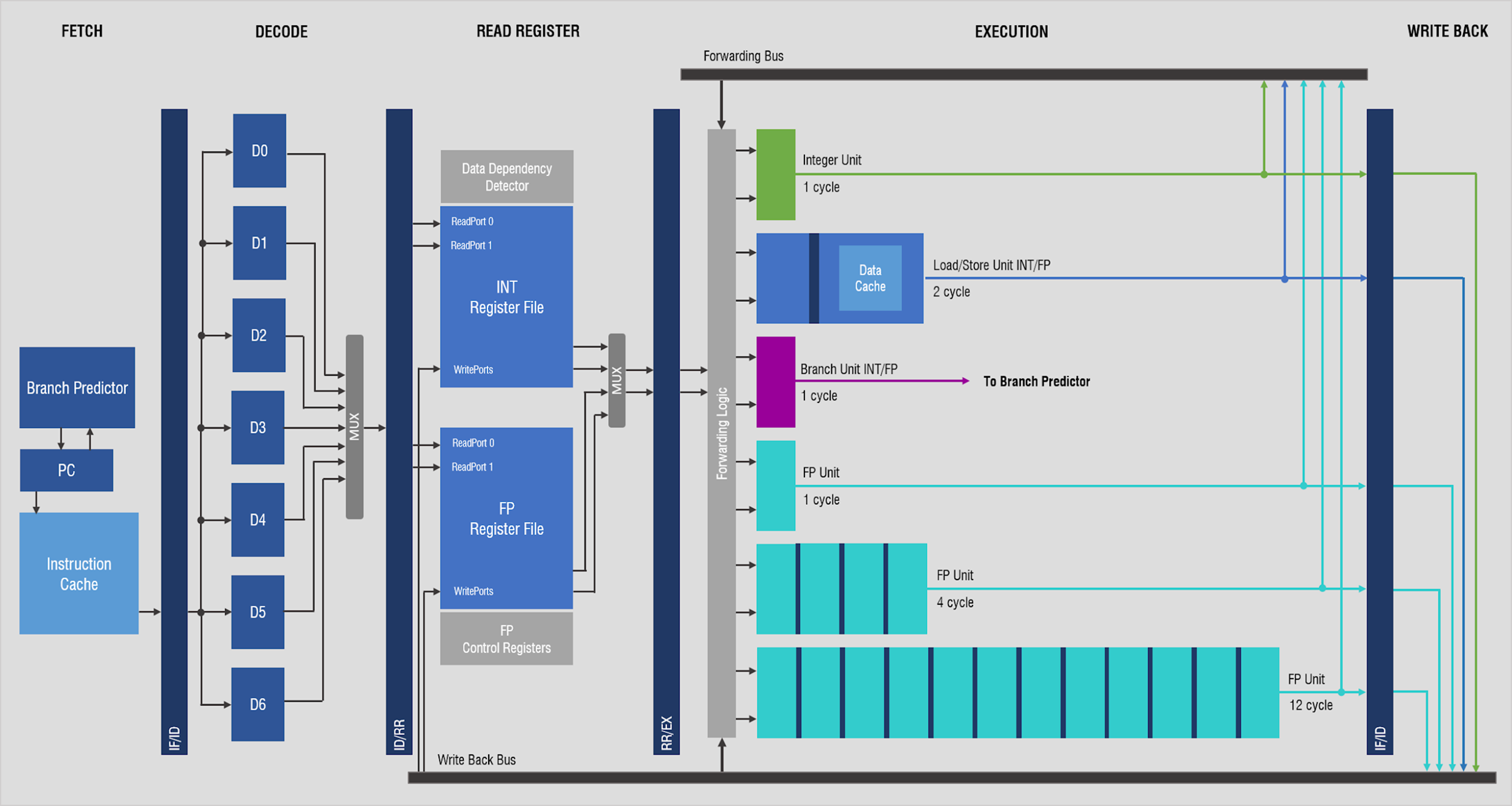

Microarquitectura del procesador Lagarto I es una arquitectura RISC segmentada de 64bits que ejecuta el conjunto de instrucciones RISC-V de operaciones con números enteros y de punto flotante en formato IEEE.

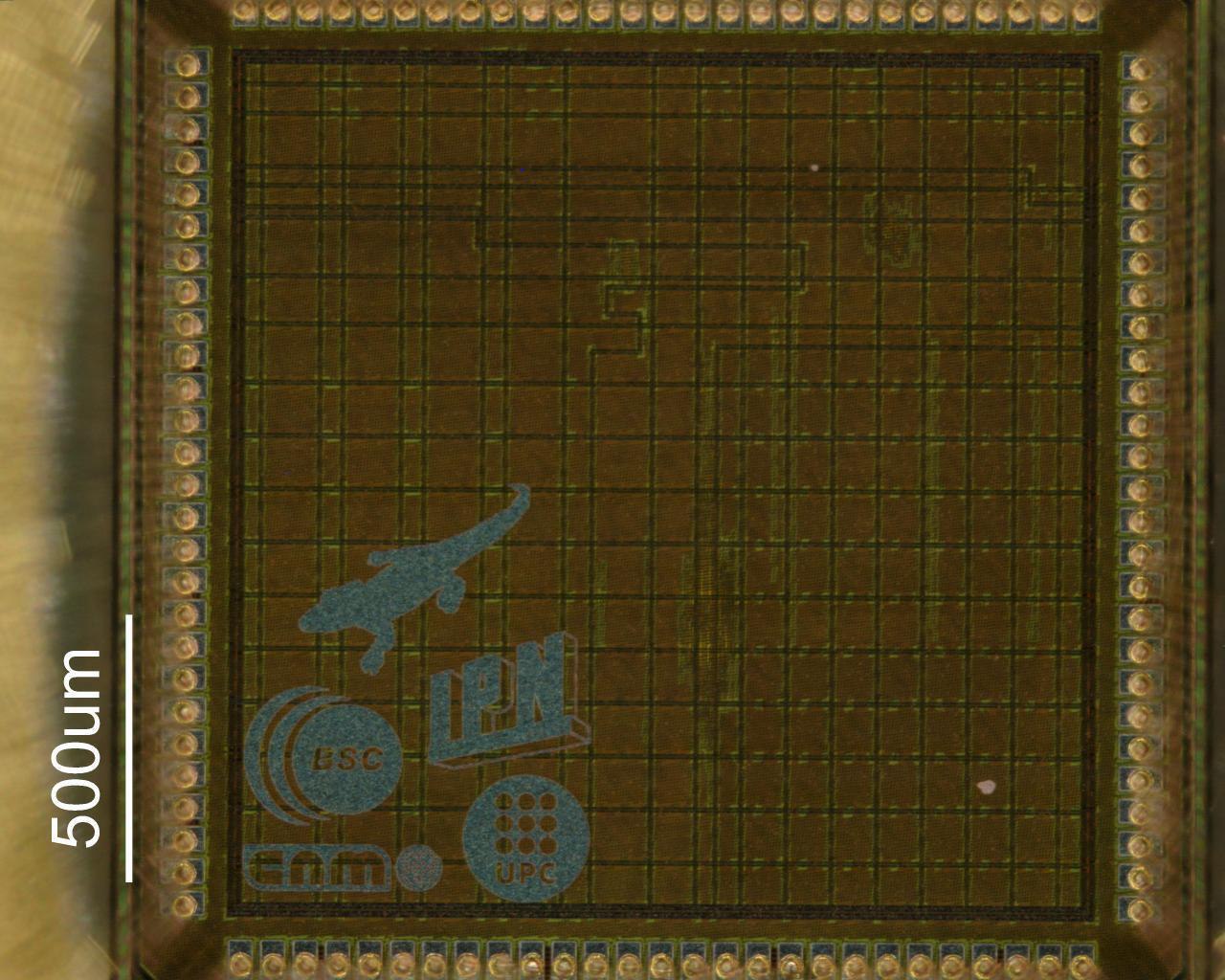

Microfotografia del Chip de Lagarto I, con tecnología de 65nm

Pruebas con ejecución de aplicaciones Bare Metal, se trata de aplicaciones de firmware que se pueden ejecutar sin la necesidad de tener un S.O. en ejecución.

Boot de Linux en Lagarto I

El video muestra cómo se realiza exitosamente el boot de Linux con Lagarto I

Lagarto I SoC Demo

Benchmark de una multiplicación de matrices.